Manjšanje proizvodnega procesa, ki je že pod 20 nanometri, je skupaj z zapisovanjem več bitov podatkov v eno celico omogočilo, da so bliskoviti (flash) pomnilniki postali dostopni. Pomanjševanje je še mogoče, v naslednjih letih lahko pričakujemo eno ali morda celo dve stopnji, nekje med 10 in 20 nm. Pod 10 nm pa naj ne bi šlo. Sosednje celice bi se med seboj preveč motile. Problem si lahko predstavljamo tudi slikovitejše. Če bi vsi ljudje stanovali v hišah, te pa bi lahko gradili le na omejenem prostoru, bi čez čas hiše postajale manjše, stale pa bi druga poleg druge. Tako skupaj, da bi se stanovalci počutili utesnjeno, hkrati pa bi jih začel motiti hrup iz sosednjih hiš. Ljudje smo problem rešili, stanovanja gradimo v višave, podobno pa naj bi bilo mogoče graditi tudi pomnilnike – v višave. Zakaj pa sploh stiskati pomnilniške celice v en čip, ko jih je lahko več? Razlog je preprost: vse v enem čipu je hitrejše, predvsem pa energetsko učinkovitejše.

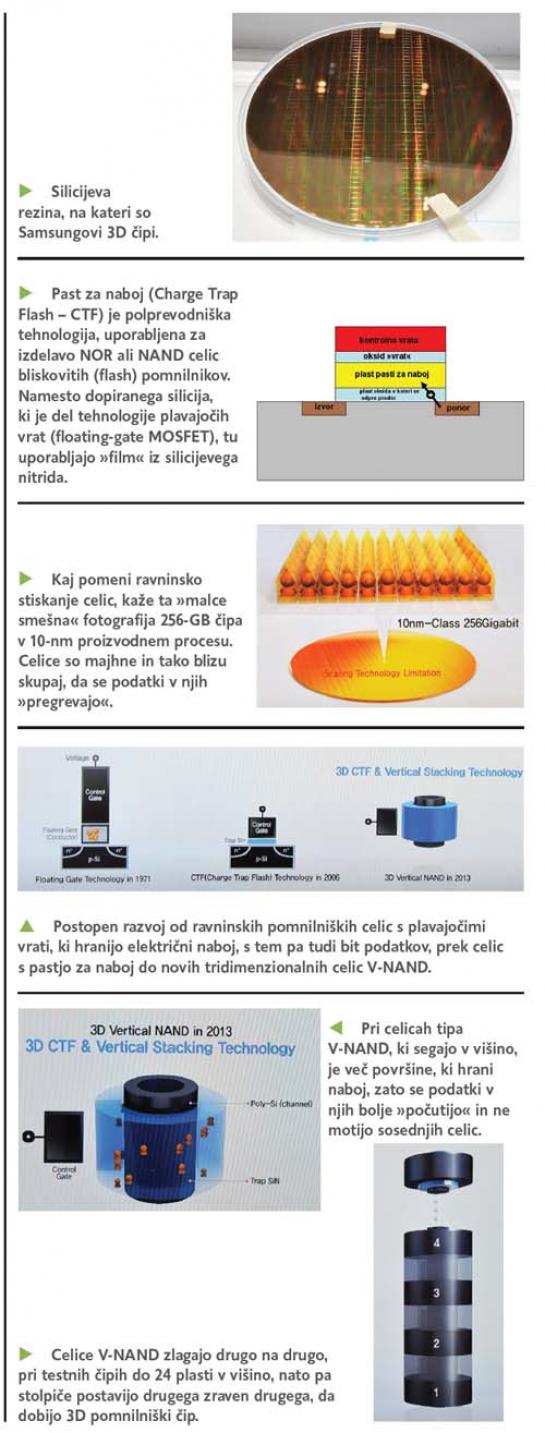

Tehnologijo gradnje pomnilnikov v višino razvija več proizvajalcev pomnilnikov, vendar je med njimi Samsung prvi, ki jih je poleti tudi komercialno ponudil. Ne sicer še za vgradnjo v mobilne naprave, to sledi v prihodnosti, temveč kot pomnilniško rešitev za strežnike. Običajne pomnilniške celice »podatek«, ki ga predstavlja električni naboj, hranijo na vratih tranzistorja (plavajoča vrata). Po določenem času uporabe se vsaka celica izrabi in ni več sposobna držati naboja (po največjem številu zapisov vanjo). Samsung je uporabil strukturo celice s tako imenovano »pastjo za naboj«, pri kateri je naboj shranjen v izolatorju, tehnologijo pa poimenoval V-NAND. Ker je problem z velikostjo tranzistorjev, so jo povečali v višino. Strukturno je zadeva videti kot vitka okrogla visoka stavba oziroma okrogel sendvič. V sredini je kanal, ki ga obkroža izolator, ki hrani naboj, okrog pa so »nameščena« vrata tranzistorjev. S tridimenzionalno mikroskopsko majhno strukturo so dosegli tudi povečanje površine snovi, ki hrani naboj, kar izboljša zanesljivost delovanja pomnilnika.

Da je pomnilniških celic v čipu dovolj, spet poskrbi višina, saj jih nalagajo drugo na drugo. Pri prvih testnih pomnilnikih so uporabili proizvodni postopek med 30 in 40 nm, kar pomeni, da so celice veliko večje, kot so pri pomnilnikih, izdelanih v 10- do 20-nm »ravninskem« procesu. Naložili so jih v 24 plasti (v višino) – prej omenjene stolpiče celic postavijo drugega poleg drugega – ter tako izdelali 128-GB pomnilniški čip. Njegova fizična velikost je približno enaka velikosti 64-GB čipa, ki je izdelan po manjšem postopku. Prednost starejšega in robustnejšega postopka je večja pomnilniška celica, ki je bolj vzdržljiva. Po besedah Samsunga naj bi celica zdržala 35 tisoč ciklov zapisov in brisanj, kar je več kot trikrat več od »običajnih« pomnilniških čipov tipa MLC (celica z več stanji). Tovrstni pomnilniki hranijo več bitov pri enakem številu tranzistorjev, kar v praksi pomeni do štiri bitov podatka v eni celici. Glede vzdržljivosti (5000) je še nekoliko slabša celica TLC oziroma celica s tremi stanji, ki pa je zanimiva zaradi svoje cene.

Moj mikro, november december 2013 | Marjan Kodelja |