Kilby in Noyce sta do iznajdb prišla neodvisno. Noyceovo integrirano vezje je bilo izdelano iz silicija in je prednik modernih čipov, Kilbyjevo pa iz germanija, ki se danes ne uporablja več.

STANDARDNE DRUŽINE ČIPOV

Prva integrirana vezja so vsebovala le nekaj deset tranzistorjev, zato so jih označili s SSI ali Small Scalle Integration, kar pomeni majhna stopnja integracije. V digitalnih čipih je bilo nekaj logičnih vrat, v analognih linearnih vezjih pa celo samo nekaj tranzistorjev. Oznako LSI ali Large Scale Integration, velika stopnja integracije, je prvi uporabil znanstvenik Rolf Landauer, ko je opisoval teoretični koncept; od tu tudi termini SSI, MSI (Medium-Scale Integration, srednja stopnja integracije), VLSI (Very Large-Scale Integration, zelo visoka stopnja integracije) in ULSI (Ultra Large-Scale Integration, ultravisoka stopnja integracije).

Vezja SSI so uporabili že v prvih vesoljskih in vojaških projektih. Tako program Apollo kot program Minuteman Missile sta potrebovala lahke digitalne računalnike za sisteme upravljanja raket. Medtem ko je bil program Apollo motivacija za razvoj tehnologije integriranih vezij, je Minuteman zahteval njihovo množično proizvodnjo. Med leti 1960 in 1963 so za programa uporabili skoraj celotno proizvodnjo integriranih vezij, katerih cena je padla z začetnih 1000 dolarjev in samo 25 dolarjev. Zato so jih začeli uporabljati tudi v izdelkih široke potrošnje, kot so radijski in televizijski sprejemniki.

Naslednja stopnja razvoja so bila vezja MSI, ki so jih začeli proizvajati v poznih šestdesetih letih in so vsebovala več sto tranzistorjev. Bila so privlačna za proizvodnjo, saj so stala le malo več kot vezja SSI, hkrati pa so se z njihovo uporabo zmanjšala in pocenila tiskana vezja, ki so lahko vsebovala manj komponent. Nadaljnji razvoj je v sredi sedemdesetih let pripeljal do čipov LSI. Imeli so okoli 10.000 tranzistorjev, uporabljali pa so jih za kalkulatorje, prve mikroprocesorje in 1-kilobitne pomnilnike.

Čipe VLSI z več 100 tisoč tranzistorji so začeli proizvajati v osemdesetih letih in jih proizvajajo še danes, ko imajo nekaj milijard tranzistorjev. Nekateri označujejo čipe z več kot milijonom tranzistorjev z oznako ULSI. Tako povečanje kompleksnosti je omogočilo več dejavnikov. Uporabljati so začeli manjša merila in čistejše proizvodne prostore, kar je omogočilo proizvodnjo manjših čipov z več tranzistorji in večjim izplenom. Izboljšala so se tudi programska orodja za načrtovanje čipov, kar je omogočilo izdelavo dizajnov v razumnem času. Energijsko učinkovitejša tehnologija CMOS je izpodrinila NMOS in PMOS.

Prve 1-megabitne pomnilnike z več kot milijonom tranzistorjev smo dobili leta 1986, mikroprocesorje z več kot milijonom tranzistorjev pa tri leta pozneje. Leto 2005 je že prineslo procesorje z milijardo tranzistorjev. Trend se nadaljuje z nezmanjšanim tempom. Tako smo leta 2007 že dobili prve pomnilniške čipe z več deset milijardami tranzistorjev.

NOVE DRUŽINE ČIPOV

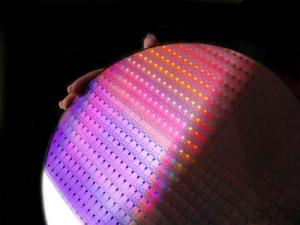

WSI (wafer-scale integration) ali integracija na osnovi rezine polprevodnika je postopek izgradnje integriranih vezij, pri katerem uporabijo celotno rezino za izdelavo enega samega »superčipa«. WSI je primerna za izdelavo superračunalnikov z visoko stopnjo vzporednosti.

Sistem na čipu (SoC ali SOC, system on chip) je integrirano vezje, pri katerem so vse potrebne komponente za računalnik vključene v enem samem čipu. Dizajn takega integriranega vezja je kompleksen in drag, saj ima lahko gradnja neenakih komponent na enem samem kosu silicija za posledico slabšo učinkovitost nekaterih elementov. Vseeno imajo računalniki v enem samem čipu prednosti, med katerimi so: manjši stroški sestavljanja naprave na tiskanem vezju in veliko manjša poraba energije, saj potekajo vsi signali med komponentami na eni sami ploščici silicija.

Trirazsežni čipi (3D-IC) imajo dva ali več nivojev aktivnih elektronskih komponent, ki so integrirane vertikalno in horizontalno v eno vezje. Komunikacija med nivoji poteka po isti silicijevi rezini, zato je poraba veliko manjša, kot bi bila pri ločenih standardnih vezjih. Dejstvo je, da lahko razumna uporaba vertikalnih vodov znatno zmanjša skupno dolžino žic in omogoči hitrejše delovanje.

TEHNOLOGIJE IZDELAVE

Proizvodnja polprevodniških integriranih vezij vključuje zaporedje fotografskih in kemijskih postopkov, med katerimi na plošči čistega polprevodnega materiala postopno nastane elektronsko vezje. Kot polprevodni material najpogosteje uporabljajo silicij. Celoten proizvodni proces od začetka obdelave silicijevih rezin do končne izdelave čipov traja od šest do osem tednov. To je tudi razumljivo, saj ima veliko modernih čipov osem ali več nivojev povezav, ki zahtevajo preko 300 proizvodnih korakov.

Tehnologije izdelave integriranih vezij pogosto ločimo le po natančnosti izdelave in jih povezujemo z razvojem mikroprocesorjev, ki so ključni gradniki sodobnih računalnikov. V začetku sedemdesetih let je Intel uporabljal 10-mikrometrski proces izdelave čipov, po katerem so izdelali legendarna mikroprocesorja 4004 in 8008. Leta 1975 so prešli na 3-mikrometrski proces, s katerim so izdelali 8085, leta 1979 pa še 8088. Razvoj je potekal naprej in leta 1982 smo dobili 80286, ki je bil izdelan po 1,5-mikrometrskem postopku. Okoli leta 1985 sta IBM in Intel osvojila 1-mikrometrsko tehnologijo in v Intelu je nastal 80386. Po 800-nanometrski (nm) tehnologiji so izdelovali Intelov 80486 in Sunov Sparc I. 600 nm tehnologija je bila razvita med leti 1994 in 1995, najbolj znani mikroprocesorji iz tega obdobja pa so: Intel 80486DX4, IBM/Motorola PowerPC 601 in Intel Pentium. Sledila je 350 nm tehnologija s Pentiumom Pro, AMD K5 in AMD K6 ter NEC VR4300, ki so ga uporabili v igralni konzoli Nintendo 64. Z 250 nm tehnologijo smo ob koncu drugega tisočletja dobili kopico novih procesorjev, med katerimi najbolj izstopajo: DEC Alpha 21264A, AMD K6-2 in K6-3D, Pentium II, Pentium MMX … 180 nm tehnologijo je v letih 1999 in 2000 osvojila večina svetovnih proizvajalcev integriranih vezij. Dobro odraža trend 70 % zmanjšanja tehnologije vsaki dve do tri leta. Po tej tehnologiji so med prvimi procesorji izdelovali tudi Pentium III Coppermine. Hkrati je to prva tehnologija, ki uporablja vrata polprevodnika, krajša od valovne dolžine svetlobe (193 nm), ki jo uporabljajo pri litografiji. Že v letih 2000 in 2001 pa smo dobili 130 nm tehnologijo, po kateri je bila izdelana kopica mikroprocesorjev (Intelovi: Pentium III, Celeron, Pentium M, Pentium 4, Xeon, AMD-jevi: Athlon XP, Athlon MP, Duron, K7 Sempron, K8 Sempron, Athlon 64, Opteron, VIA: C3 …).

90 nm tehnologija pomeni prelomnico pri procesu množične proizvodnje integriranih vezij, saj so s to tehnologijo prešli z 200 mm na 300 mm silicijeve rezine. Uporabljati so jo začeli v letih 2002 in 2003. Po 90 nm tehnologiji je izdelano veliko Intelovih in AMD-jevih procesorjev, od Pentiuma 4, Celerona D, Xeona, do Athlona 64, Semprona, Turiona 64 … Naslednja je 65 nm tehnologija, ki so jo leta 2007 uvedli pri večini proizvajalcev čipov. Medtem, ko so elementi integriranega vezja veliki 65 nm ali manj, uporabljajo pri fotolitografiji svetlobo z valovnima dolžinama 193 nm in 248 nm. To zahteva uporabo posebnih tehnologij prenosa slike, kot sta optična korekcija bližine in maske za fazni premik. Podobno kot 65 nm tehnologija, tudi 45 nm tehnologija zahteva uporabo posebnih fotolitografskih postopkov. Prva sta jo konec leta 2007 uvedla Matsushita in Intel. Leto pozneje so sledili še drugi proizvajalci, med njimi AMD, IBM, Samsung … Pri Matsushiti so izdelali sistem na čipu za potrošniško elektroniko. Prvi Intelov procesor, Xeon-5400, izdelan po 45 nm tehnologiji pa je prišel na trg novembra 2007. AMD po 45 nm tehnologiji izdeluje Phenom II in Shanghai Opteron.

PRIHAJAJOČE TEHNOLOGIJE

Zmanjševanje dimenzij tranzistorjev se bo v prihodnjih letih nadaljevalo. Pri Intelu so že osvojili 32 nm tehnologijo in po njej izdelali prvi statični pomnilnik. Za konec tega leta načrtujejo tudi prvi mikroprocesor. Vendar to ni konec razvojne poti.

Naslednji korak, 22 nm tehnologijo, lahko pričakujemo med leti 2011 in 2012. Strokovnjaki trenutno vidijo težavo pri fizični debelini izolacijskega oksida, ki ne more biti manjša od 0,5 nm, kar je potrebno pri 22 nm tranzistorju. Kaže, da je s tem zmanjševanje vezij CMOS prišlo do nepremostljive ovire. Zanimive so tudi druge napovedi za 22 nm integrirana vezja. Silicijevi tranzistorji ne bodo več planarni, ampak bodo sestavljeni iz ultratankih sekcij, obkroženih z vrati. Sekcije bodo štrlele iz površine kot plavuti (angl. fins). Zato so tovrstna vezja označili z oznako FinFET. Pomembna prelomnica pri izdelavi integriranih vezij je tudi, da bo prvič uporabljen porozni dielektrični material z nizko dielektrično konstanto, ki bo nadomestil tradicionalni gostejši silicijev dioksid.

Zadnja v vrsti tehnologij je 16 nm tehnologija, za katero pričakujejo, da se bo pojavila okoli leta 2018. Če pa bo tehnološki razvoj tako hiter, kot predvidevajo v Intelu, jo bodo dosegli že leta 2013. Znanstveniki menijo, da nadaljnje pomanjševanje tehnologije izdelave silicijevih tranzistorjev ne bo mogoče zaradi učinka kvantnega tuneliranja, ne glede na to, katere materiale bodo uporabili. Kakorkoli, trenutno je zelo malo predmetov, ki jih lahko izdelajo v velikosti 16 nm v velikih količinah. Za primerjavo povejmo, da je razdalja med neraztegnjenimi silicijevimi atomi 0,543 nm, kar pomeni, da bi kanal 16 nm tranzistorja CMOS tvorilo manj kot trideset atomov. To bi imelo za posledico znatno »puščanje« tranzistorja in z njim povezano porabo energije, ki bi povzročila prekomerno segrevanje čipa. Pričakujejo, da bodo razvijalci prisiljeni uporabiti eksotične tehnologije, ki ne temeljijo na siliciju. Zato naj bi 16 nm tehnologija napovedovala prelom med tehnologijo CMOS in nanoelektroniko.

Koraki izdelave čipa

• Obdelava rezine polprevodnega materiala

mokro čiščenje

fotolitografija

nanos ionov (s katerim vnesejo nečistoče v polprevodniško ploščo in ustvarijo področja s povečano ali zmanjšano prevodnostjo)

suho jedkanje

mokro jedkanje

odstranjevanje fotozaščitnega nanosa

toplotna obdelava

izpostavitev kemični pari

izpostavitev vakuumu

molekularna žarkovna epitaksija

elektrokemični nanos

kemično-mehansko poliranje

testiranje rezine (preverjanje električnih karakteristik)

stanjšanje rezine z brušenjem (za zmanjšanje debeline čipa, kar omogoča, da ga uporabimo v tankih napravah, npr. smartcard in PCMCIA)

• Priprava ploščic z integriranimi vezji

pritrditev rezine

razrez rezine na ploščice z integriranimi vezji

• Pakiranje ploščic z integriranimi veziji

pritrditev ploščice z integriranim vezjem na ohišje

povezovanje integriranih vezij s kontakti na ohišjih

zapiranje integriranih vezij

• Testiranje čipov

Moj mikro, december 2009 | Piše: dr. Simon Vavpotič